���]ϵ�y(t��ng)���d��� ����Windows10ϵ�y(t��ng)���d ����Windows7ϵ�y(t��ng)���d xpϵ�y(t��ng)���d ��X��˾W(w��ng)indows7 64λ�b�C(j��)�f(w��n)�ܰ����d

��Modelsim�e�桿Modelsim SE���d v10.7 �h���e��(�����b�̳�)

- ܛ����ͣ�����ܛ��

- ܛ���Z(y��)�ԣ���(ji��n)�w����

- �ڙ�(qu��n)��ʽ�����M(f��i)ܛ��

- ���r(sh��)�g��2024-12-13

- ��x��(sh��)����

- ���]�Ǽ�(j��):

- �\(y��n)�Эh(hu��n)����WinXP,Win7,Win10,Win11

ܛ����B

Modelsim�e����һ����Mentor��˾�_(k��i)�l(f��)��HDL�Z(y��)�Է���ܛ����������Ҫ���þ��Ǟ��Ñ��ṩ�Ѻõķ���h(hu��n)�����҂�����ͨ�^(gu��)ʹ��Modelsim�h������ķ�������(l��i)���HDL�Z(y��)�Եķ��澎�g�����������@��ܛ��ͬ�r(sh��)����SE��PE��LE��OEM�ȶ�N�汾���Ñ����������x��

Modelsim�e��ܛ����(ji��n)��

Mentor��˾��ModelSim�ǘI(y��)���(y��u)���HDL�Z(y��)�Է���ܛ���������ṩ�Ѻõķ���h(hu��n)�����ǘI(y��)��Ψһ�Ć�(n��i)��֧��VHDL��Verilog��Ϸ���ķ�������������ֱ�Ӄ�(y��u)���ľ��g���g(sh��)��Tcl/Tk���g(sh��)���͆�һ��(n��i)�˷��漼�g(sh��)�����g�����ٶȿ죬���g�Ĵ��a�cƽ�_(t��i)�o(w��)�P(gu��n)�����ڱ��o(h��)IP�ˣ���(g��)�Ի��ĈD�ν�����Ñ��ӿڣ����Ñ��ӿ��{(di��o)�e(cu��)�ṩ��(qi��ng)�������ֶΣ���FPGA/ASIC�O(sh��)Ӌ(j��)�����x����ܛ����

ܛ����ɫ

· RTL���T(m��n)��(j��)��(y��u)�������ؾ��g�Y(ji��)��(g��u)�����g�����ٶȿ죬��ƽ�_(t��i)��汾���棻

· ��(n��i)��VHDL��Verilog��Ϸ��棻

· Դ���aģ������֣��(xi��ng)Ŀ������

· ���������ܷ��������α��^�����a���w����(sh��)��(j��)��ChaseX��Signal Spy��̓�M��(du��)��Virtual Object��Memory���ڡ�Assertion���ڡ�Դ�a�����@ʾ��̖(h��o)ֵ����̖(h��o)�l�����c(di��n)�ȱ����{(di��o)ԇ���ܣ�

· C��Tcl/Tk�ӿڣ�C�{(di��o)ԇ��

· ��(du��)SystemC��ֱ��֧�֣���HDL�����ϣ�

· ֧��SystemVerilog���O(sh��)Ӌ(j��)���ܣ�

· ��(du��)ϵ�y(t��ng)��(j��)�����Z(y��)�Ե���ȫ��֧�֣�SystemVerilog��SystemC��PSL��

· ASIC Sign off��

· ���ԆΪ�(d��)��ͬ�r(sh��)�M(j��n)���О飨behavioral����RTL��(j��)�����T(m��n)��(j��)��gate-level���Ĵ��a��

Modelsim�e�湦�ܽ�B

1����(j��)���a���w��

ModelSim�ĸ�(j��)���a���w���ܺ������Խ����������@һ���F�(y��n)�C�YԴ���ϵK��

ModelSim��(j��)���a���w���ܞ�ϵ�y(t��ng)�(y��n)�C�ṩ���Ѓr(ji��)ֵ��ָ��(bi��o)�� ���и��w��Ϣ���惦(ch��)�ڽy(t��ng)һ���w��(sh��)��(j��)��(k��)��UCDB���У�ԓ��(sh��)��(j��)��(k��)�����ռ�������Ч��(sh��)��(j��)��(k��)�е����и��w��Ϣ�� ����ʹ�÷������a���w�ʔ�(sh��)��(j��)�ĸ��w�ʌ�(sh��)�ó�������ϲ��͜y(c��)ԇ������ ���w�Y(ji��)�����Խ���ʽ�鿴��ģ�M�����ģ�M�\(y��n)�кϲ���鿴�� ���a���w����������(sh��)�����O(sh��)Ӌ(j��)��λ��(b��o)�棬�Ķ��ṩ�������w��(sh��)��(j��)���`���ԡ�

֧�ֵĸ��w��Ͱ�����

����(b��o)��

�\(y��n)�����g��(zh��)�е��Z(y��)�䔵(sh��)

���Ј�(b��o)��

Ӱ�HDL��(zh��)�п������ı��_(d��)ʽ��case�Z(y��)��

�l�����w

����֧�ϵėl���ֽ��ʹ�Y(ji��)����true��false��Ԫ��

���_(d��)����

�c�l�����w��ͬ�������w���l(f��)��̖(h��o)��������Ƿ�֧�Q��

���c(di��n)�P(gu��n)ע���_(d��)

�Դ_�����w�Y(ji��)���ı��_(d��)ʽ��ÿ��(g��)��(d��)��ݔ��ķ�ʽ�ʬF(xi��n)���_(d��)���w�ʔ�(sh��)��(j��)

����(qi��ng)���ГQ���w����

��Ĭ�J(r��n)ģʽ�£�Ӌ(j��)��(sh��)�ĵ͵��ߺ͏ĸߵ��͵��D(zhu��n)�Q;�ڔU(ku��)չģʽ�£�Ӌ(j��)���cX���D(zhu��n)�Q

���ޠ�B(t��i)�C(j��)���w

�ݺ��ݵ��^(gu��)�ɸ��w����

2�����HDL����

ModelSim���������ܺ������cģ�M����(g��)ģ�K��ϵ�y(t��ng)�Լ���(sh��)�F(xi��n)ASIC�T(m��n)��(j��)�e��������Ĵ��a���w���{(di��o)ԇ������Y(ji��)�ϡ� ȫ��֧��Verilog��SystemVerilog for Design��VHDL��SystemC����Z(y��)�ԺͶ��Z(y��)���O(sh��)Ӌ(j��)�(y��n)�C�h(hu��n)���ṩ�ˈ�(ji��n)��(sh��)�Ļ��A(ch��)�� ModelSim����ʹ���ҽy(t��ng)һ���{(di��o)ԇ�ͷ���h(hu��n)���鮔(d��ng)���FPGA�O(sh��)Ӌ(j��)�ˆT�ṩ�������������L(zh��ng)�ĸ�(j��)�����Լ�ʹ�����Ĺ�����Ч�ĭh(hu��n)����

3����Ч���{(di��o)ԇ�h(hu��n)��

ModelSim�{(di��o)ԇ�h(hu��n)����Verilog��VHDL��SystemC�ṩ�ˏV����ֱ�^���ܣ�ʹ��ɞ�ASIC��FPGA�O(sh��)Ӌ(j��)�����x��

ModelSimͨ�^(gu��)�����O(sh��)Ӌ(j��)���{(di��o)ԇ�h(hu��n)����(ji��n)���˰l(f��)�F(xi��n)�O(sh��)Ӌ(j��)ȱ�ݵ��^(gu��)�̡� ModelSim�{(di��o)ԇ�h(hu��n)����Ч���@ʾ�O(sh��)Ӌ(j��)��(sh��)��(j��)���Ա�������{(di��o)ԇ�����Z(y��)�ԡ�

ModelSim���S�ڱ���Y(ji��)���ķ�����Լ���(sh��)�r(sh��)�����\(y��n)�����gʹ���S���{(di��o)ԇ�ͷ������ܡ����磬coverage�鿴��ʹ�ô��a���w�ʽY(ji��)��������ע�Դ���a������FSM��B(t��i)���D(zhu��n)�Q���Z(y��)�䣬���_(d��)ʽ����֧���ГQ���w�ʡ�

��̖(h��o)ֵ������Դ������עጲ��ڲ��β鿴���в鿴���Ķ���(ji��n)���ˌ�(du��)������֮�g�Լ��L��(w��n)�ļ�֮�g�ij�朽ӌ�(d��o)�����{(di��o)ԇ��(d��o)����

�������б��Ͳ��δ����з�����(j��ng)��(zh��ng)�l�����������¼����(d��ng)�������p�ɶ��x�Ñ����x��ö�eֵ���Ա������˽�ģ�M�Y(ji��)������������{(di��o)ԇЧ�ʣ�ModelSim߀���ЈD�κ��ı���(sh��)��(j��)�����ܡ�

ModelSim�cMentor����Ş?z��i)��M��Questa?����һ��(g��)��ͬ��ǰ�˺��Ñ����档�@ʹ�͑������p������(j��)��Questa����?y��n)�������Ҫ���ߵ����ܲ�֧�ָ?j��)�(y��n)�C���ܡ�

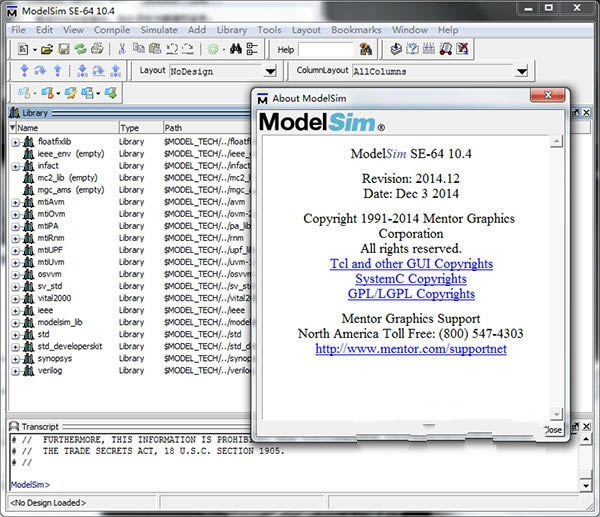

Modelsim�e�氲�b���E

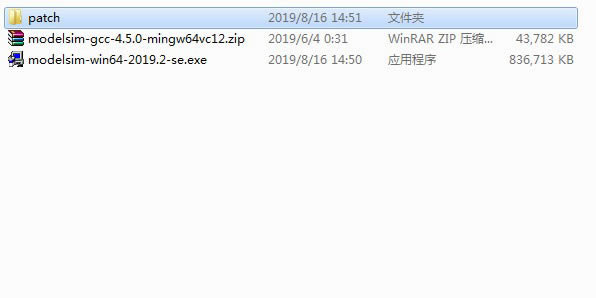

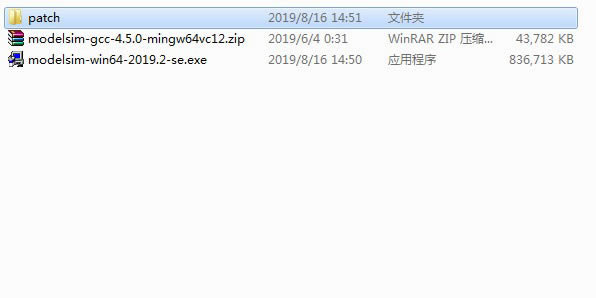

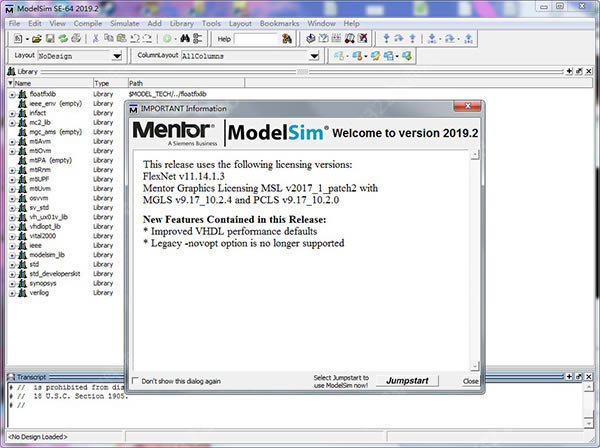

1�����d�≺���õ�modelsim se 2019.2 64λԭ�����patch�e�ļ��A��

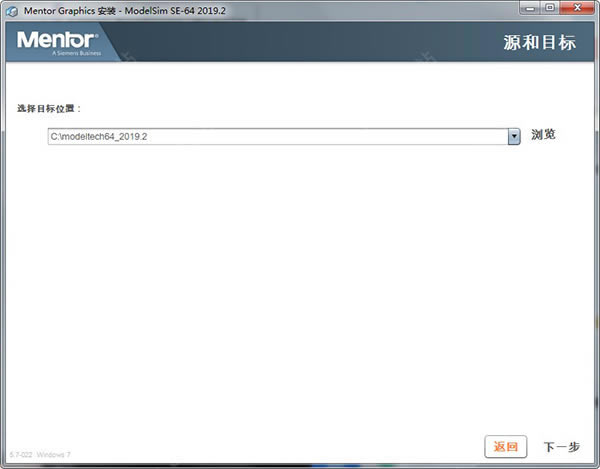

2�������p���ļ�“modelsim-win64-2019.2-se.exe”���bܛ������Ĭ�J(r��n)·�����b���ɣ�

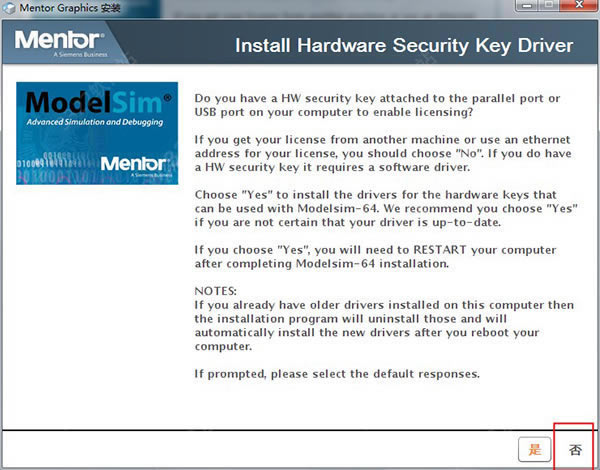

3��ע�⣺�@һ����Ҫ���bKey Driver��

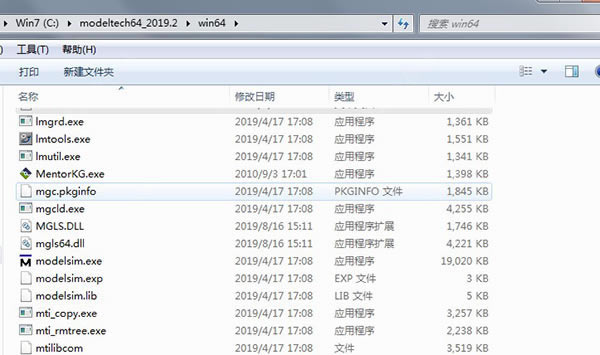

4��ܛ���ɹ����b���Ȳ��\(y��n)��ܛ�������_(k��i)patch�e�ļ��A����MentorKG.exe��MGLS.DLL��patch_dll.bat��(f��)�Ƶ����bĿ��µ�win64�ļ��A�У�Ĭ�J(r��n)·����C:\modeltech64_2019.2\win64��

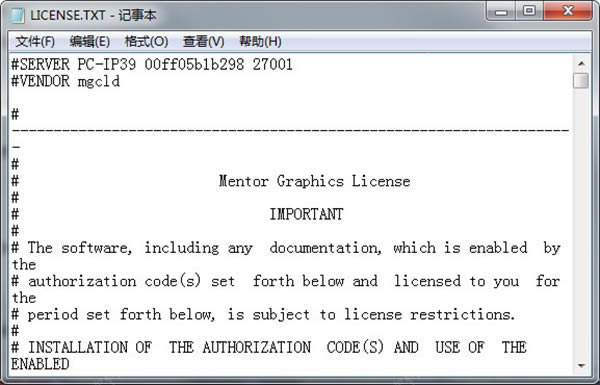

5���\(y��n)��patch_dll.bat�������ɵ��S���C�����L(zh��ng)ICENSE.TXT����ñ��浽ܛ�����bĿ��£�

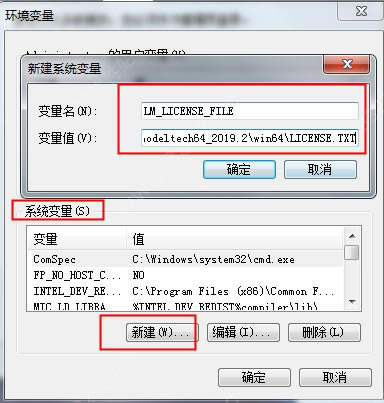

6������(l��i)����(chu��ng)��ϵ�y(t��ng)�h(hu��n)��׃����

׃������LM_LICENSE_FILE

׃��ֵ��LICENSE.TXT��·����

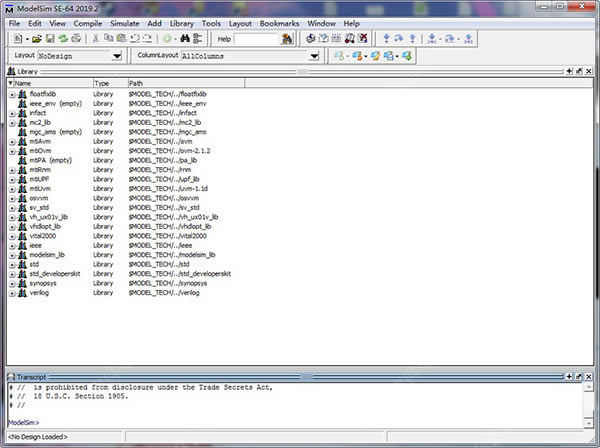

7�����ˣ�ܛ���ɹ�������Ͼ���modelsim se 2019.2 64λ�e���Ԕ��(x��)���b�̳̣�ϣ����(du��)�Ñ��Ў�����

Modelsim�e��ʹ�ü���

modelsim����½����̺̈́�(chu��ng)���ļ���

����(d��ng)modelsim���ҵİ汾��6.5b����ͬ�汾���ܽ�����߲������E��ͬ�����ǿ��Թ�����Á�(l��i)�����W(xu��)��(x��)����Ҳ���Ե����bĿ����M(j��n)�І���(d��ng)�x�����(hu��)�������ߙ����кܶ���x�(xi��ng)����ҵ��x��

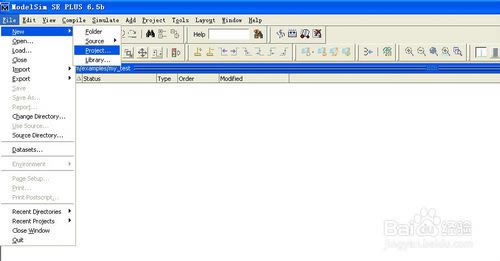

�x�����Ͻǵ�file-project-new project���ļ�-����-�½������x��Ȼ���M(j��n)�����P(gu��n)�Ľ��棬���(hu��)����Ҫ�½����̵Ľ��档

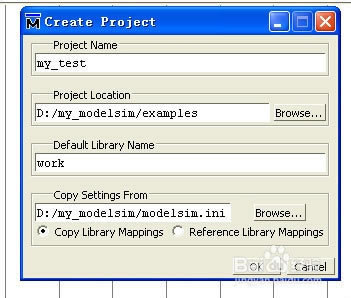

��Ҫ�½����̵Ľ�����ݔ�����½����̵����Q�Լ������Ŀ䛣��@��(g��)�ط���Ҫ�O(sh��)�úã�ע���O(sh��)�õ�Ŀ䛺������Q������������M(j��n)�Ќ��ҡ�

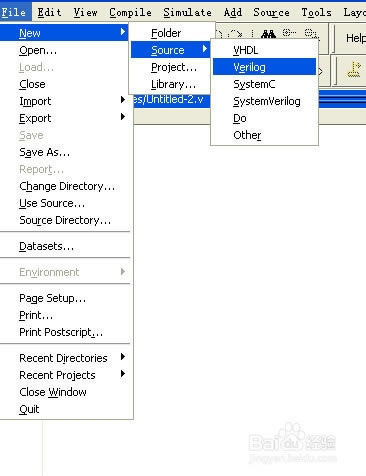

���½������ꮅ�����½�verilog�ļ������ھ���(xi��)���̴��a���ߜy(c��)ԇ���a����Ȼ����@Щ�ļ����뵽��(d��ng)ǰ�Ĺ��̣��x��new-source-verilog��Ȼ����½����ļ���

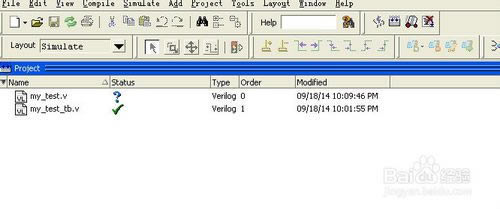

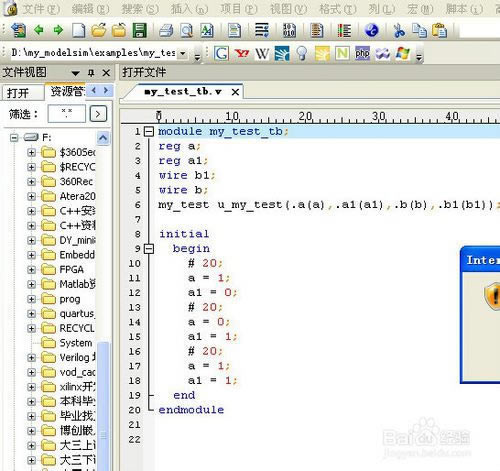

���������½��ăɂ�(g��)�ļ�����Ҫ���ڜy(c��)ԇ�c���T(m��n)�Ĺ��ܣ�Ȼ��������M(j��n)���������ܴ��a�ľ�������֮��e���˱��档

�������Ҍ�(xi��)�ĺ�(ji��n)�ε�verilog���a���Á�(l��i)�o���ʾ�⣬�����(hu��)�v����M(j��n)�й��ܵķ��棬�鿴���Ρ�

1�M���ƽ̌W(xu��)ͨ2.0-�M���ƽ̌W(xu��)ͨ2.0���d v5......

2step7 microwin-���T(m��n)��PLC S7......

3�ٶȾW(w��ng)�P(p��n)��ˬ����(ji��n)������-�W(w��ng)�P(p��n)����-�ٶȾW(w��ng)�P(p��n)��ˬ��......

4360��ȫ�g�[��-�g�[��-360��ȫ�g�[�����d ......

5�ȸ�g�[�� XP��-�ȸ�g�[�� XP��-�ȸ�g�[......

6Kittenblock�ؑc�������ð�-�C(j��)���˾���......

7seo�������(����(j��)���) -SEO��會�(y��u)������......

8Notepad3-ӛ�±�ܛ��-Notepad3��......

9С���\(y��n)��(d��ng)ˢ����(sh��)����-С���\(y��n)��(d��ng)ˢ����(sh��)�������d v2......

1����\(y��n)��GHOST���bϵ�y(t��ng),��������\(y��n)���R���b�C(j��)

2Ů����ɶ���^��ã��m��Ů���\(y��n)�õ����^��_��

3���Ľ�����ΰ��bghostxpϵ�y(t��ng)

4�o(w��)�����(bi��o)�p�ĵĎNԭ�� �Լ�̎������

5Windows��������(j��)Win10ʧ����ʾ0x80...

6����(j��)Windows10 1607�汾�ľ��w�O(sh��)�÷�...

7win10��X�桶ֲ����(zh��n)��ʬ���W�˵�̎���k��

82018������^����ɶ��2018���Ů��...