���]ϵ�y(t��ng)���d��� ����Windows10ϵ�y(t��ng)���d ����Windows7ϵ�y(t��ng)���d xpϵ�y(t��ng)���d ��X��˾W(w��ng)indows7 64λ�b�C(j��)�f�ܰ����d

��Modelsim�e�����d��Modelsim�e�� v10.1 ���w����

- ܛ����ͣ�����ܛ��

- ܛ���Z�ԣ����w����

- �ڙ�(qu��n)��ʽ�����M(f��i)ܛ��

- ���r�g��2024-12-06

- ��x��(sh��)����

- ���]�Ǽ�:

- �\(y��n)�Эh(hu��n)����WinXP,Win7,Win10,Win11

ܛ����B

Modelsim�e����һ���ʮ�֏�(qi��ng)��ľ��̾��gܛ����������(y��u)���HDL�Z�Է��湦�ܣ�����ʹ�á��y(t��ng)һ�{(di��o)ԇ��֧��VHDL��Verilog��SystemVerilog�ȶ�N����Z�ԣ��ṩȫ�������Լ������ܵ��(y��n)�C���ܣ�����������ģʽ�\(y��n)�С�

ܛ����ɫ

1���y(t��ng)һ�Ļ���Z��ģ�M���棬����ʹ�ú�����

2��֧�ֵ�Verilog��SystemVerilog���O(sh��)Ӌ��VHDL��SystemC����(f��)�s���O(sh��)Ӌ�h(hu��n)������Ч�˲�

3�������{(di��o)ԇ������ʹ�ã����Z���{(di��o)ԇ�h(hu��n)��

4�������a���w�ͷ��� ���ߣ��ɿ��ٸ��w����

5������ʽ�ͺ���ģ�M�{(di��o)ԇ���ã���˃��߶�ʹ����ͬ���{(di��o)ԇ�h(hu��n)��

6��Modelsim�e�揊(qi��ng)��IJ��� ���^�����ڷ�������e�`

7���y(t��ng)һ���w��(sh��)��(j��)�죬���������Ľ���ʽ��HTML����̎�����ܣ������������(xi��ng)Ŀ��������{(di��o)ԇ���w��

8���cHDL Designer��HDL Author��Y(ji��)�ϣ��Ɍ�(sh��)�F(xi��n)�������O(sh��)Ӌ��(chu��ng)�����(xi��ng)Ŀ�����Ϳ�ҕ������

ܛ������

һ�������a���w��

ModelSim�ĸ����a���w���ܺ������Խ����������@һ���F�(y��n)�C�YԴ���ϵK��

ModelSim�����a���w���ܞ�ϵ�y(t��ng)�(y��n)�C�ṩ���Ѓrֵ��ָ��(bi��o)�����и��w��Ϣ���惦�ڽy(t��ng)һ���w��(sh��)��(j��)�죨UCDB���У�ԓ��(sh��)��(j��)�������ռ�������Ч��(sh��)��(j��)���е����и��w��Ϣ������ʹ�÷������a���w�ʔ�(sh��)��(j��)�ĸ��w��(sh��)�ó�������ϲ��͜yԇ���������w�Y(ji��)�����Խ���ʽ�鿴��ģ�M�����ģ�M�\(y��n)�кϲ���鿴�����a���w����������(sh��)�����O(sh��)Ӌ��λ��棬�Ķ��ṩ�������w��(sh��)��(j��)���`���ԡ�

�������HDL����

ModelSim���������ܺ������cģ�M����ģ�K��ϵ�y(t��ng)�Լ���(sh��)�F(xi��n)ASIC�T���e��������Ĵ��a���w���{(di��o)ԇ������Y(ji��)�ϡ�ȫ��֧��Verilog��SystemVerilog for Design��VHDL��SystemC����Z�ԺͶ��Z���O(sh��)Ӌ�(y��n)�C�h(hu��n)���ṩ�ˈԌ�(sh��)�Ļ��A(ch��)��ModelSim����ʹ���ҽy(t��ng)һ���{(di��o)ԇ�ͷ���h(hu��n)���鮔(d��ng)���FPGA�O(sh��)Ӌ�ˆT�ṩ�������������L�ĸ������Լ�ʹ�����Ĺ�����Ч�ĭh(hu��n)����

������Ч���{(di��o)ԇ�h(hu��n)��

ModelSim�{(di��o)ԇ�h(hu��n)����Verilog��VHDL��SystemC�ṩ�ˏV����ֱ�^���ܣ�ʹ��ɞ�ASIC��FPGA�O(sh��)Ӌ�����x��

ModelSimͨ�^�����O(sh��)Ӌ���{(di��o)ԇ�h(hu��n)�������˰l(f��)�F(xi��n)�O(sh��)Ӌȱ�ݵ��^�̡�ModelSim�{(di��o)ԇ�h(hu��n)����Ч���@ʾ�O(sh��)Ӌ��(sh��)��(j��)���Ա�������{(di��o)ԇ�����Z�ԡ�

ModelSim���S�ڱ���Y(ji��)���ķ�����Լ���(sh��)�r�����\(y��n)�����gʹ���S���{(di��o)ԇ�ͷ������ܡ����磬coverage�鿴��ʹ�ô��a���w�ʽY(ji��)��������ע�Դ���a������FSM��B(t��i)���D(zhu��n)�Q���Z�䣬���_(d��)ʽ����֧���ГQ���w�ʡ�

��ֵ̖������Դ������עጲ��ڲ��β鿴���в鿴��ͨ�^��������֮�g�Լ��L���ļ�֮�g�ij�朽ӌ�(d��o)�������{(di��o)ԇ��(d��o)����

�������б��Ͳ��δ����з��������l�����������¼���ӡ������p�ɶ��x�Ñ����x��ö�eֵ���Ա������˽�ģ�M�Y(ji��)������������{(di��o)ԇЧ�ʣ�ModelSim߀���ЈD�κ��ı���(sh��)��(j��)�����ܡ�

ModelSim�cMentor����Ş?z��i)��M��Questa����һ����ͬ��ǰ�˺��Ñ����档�@�ӣ�����͑���Ҫ���ߵ����ܲ�֧�ָ��(y��n)�C���ܣ��t�����p��������Questa��

Modelsim�e������

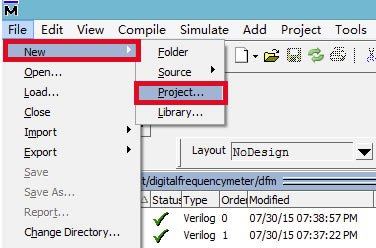

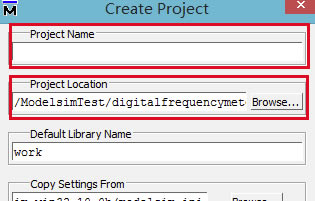

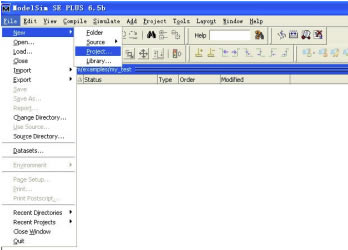

1���Γ�File�������(bi��o)����New���x��Project...�����F(xi��n)��D��ʾ�Č�Ԓ����߅�ļt�����Ҫ�����Ĺ������Q�������҂�Ҫ�c(di��n)��һ��led���ͽ���һ����������led�Ĺ��̡���߅�ļt����ָ��Ҫ�ѹ��̽�����ʲôλ�á�������x�(xi��ng)Ĭ�J(r��n)���ɡ��c(di��n)��ok��

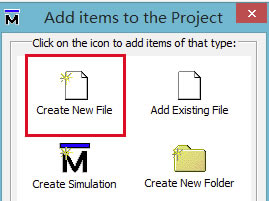

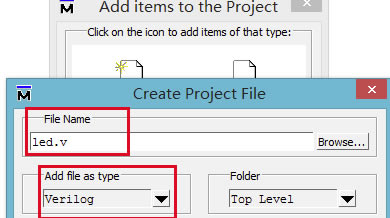

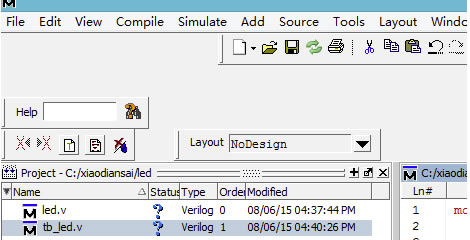

2���������c(di��n)��Create new File���ڏ����Č�Ԓ������ļ���������led.v��add file as type���x��verilog���c(di��n)��ok����?y��n)��҂�Ҫ��Modelsim���棬һ��Ҫ�Мyԇ�ļ���������һ�����ɣ�������led.v���Eһ�ӡ���������tb_led.v��

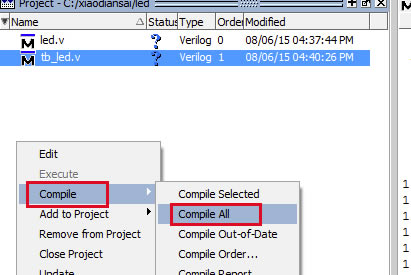

3���քe�p���ļ������M(j��n)�뾎ģʽ���������a����������(bi��o)��������һ���ļ������I��compile->compile all�����gͨ�^����ʾ

# Compile of tb_led.v was successful.

# 2 compiles, 0 failed with no errors.

�Ϳ����M(j��n)�з����ˡ�

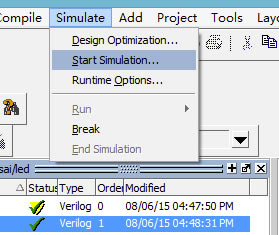

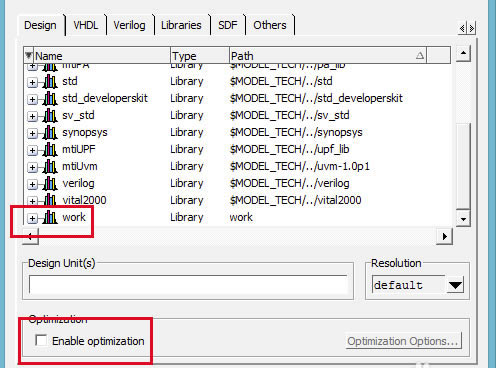

4���c(di��n)��Simulate->start Simulation��ӛ�ð�optimizationqian2�Ĺ��xȥ�����c(di��n)��workǰ�ļ�̖���x��yԇ�ļ��������Ҍ�����tb_led.v��ok��

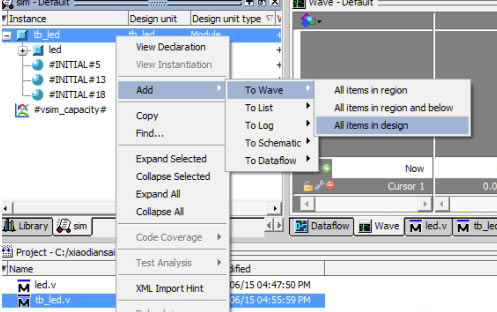

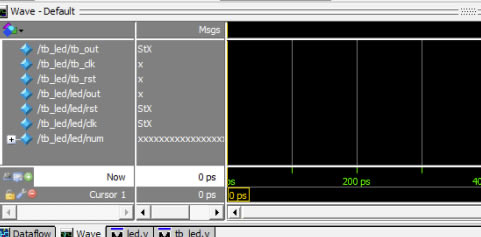

���F(xi��n)wave���F(xi��n)�ڰѲ��μ��M(j��n)ȥ���� tb_led�ļ����I Add->To wave ->All items in design���_ʼ�\(y��n)�з��棬�c(di��n)����һ������߅���p���^�ĈD��(bi��o)�����c(di��n)���Ŵ��R�����{(di��o)��(ji��)���εĕr�g�S������(bi��o)�����ķ��沨����D��ϣ�����ゃ�Ў�����

Modelsim�e�����_����

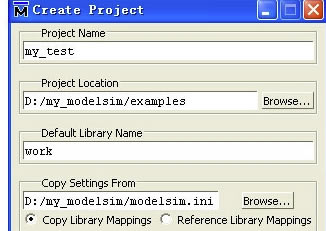

1���x�����Ͻǵ�file-project-new project���ļ�-����-�½������x��Ȼ���M(j��n)�����P(gu��n)�Ľ��棬�������Ҫ�½����̵Ľ��档

2����Ҫ�½����̵Ľ�����ݔ�����½����̵����Q�Լ������Ŀ䛣��@���ط���Ҫ�O(sh��)�úã�ע���O(sh��)�õ�Ŀ䛺������Q������������M(j��n)�Ќ��ҡ�

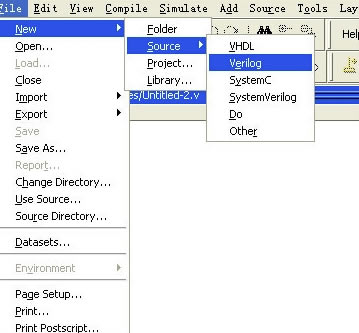

3�����½������ꮅ�����½�verilog�ļ������ھ������̴��a���ߜyԇ���a����Ȼ����@Щ�ļ����뵽��(d��ng)ǰ�Ĺ��̣��x��new-source-verilog��Ȼ����½����ļ���

4�����������½��ăɂ��ļ�����Ҫ���ڜyԇ�c���T�Ĺ��ܣ�Ȼ��������M(j��n)���������ܴ��a�ľ�������֮��e���˱��档

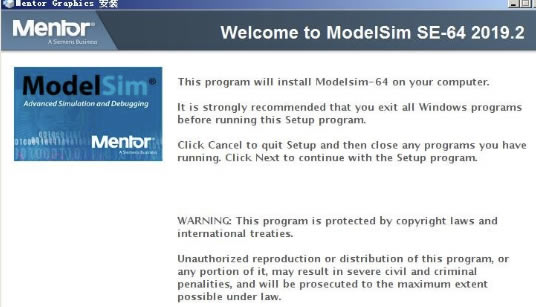

Modelsim�e�氲�b����

1���ڱ�վ���dModelsim�e�氲�b��

2��ʹ�É��sܛ���M(j��n)�н≺�����]ʹ��winrar��

3���c(di��n)��exe�ļ��_ʼ���b

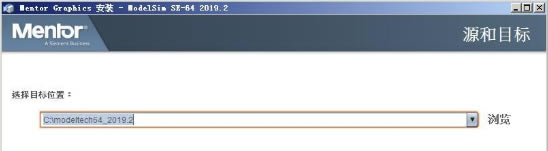

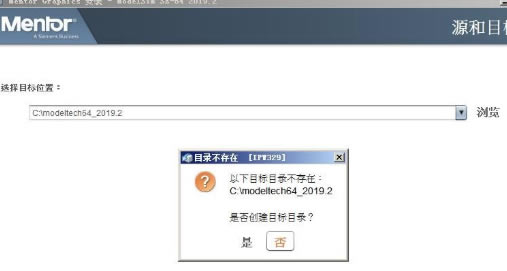

4���x��ܛ�����bĿ䛣�Ĭ�J(r��n)��“C:\modeltech64_2019.2”��Ҳ�����c(di��n)�g�[�ģ�Ȼ���c(di��n)��һ��

5������(j��)��ʾ��(chu��ng)��Ŀ䛣��c(di��n)next

6�������f(xi��)�h���棬�м�(x��)��x���c(di��n)ͬ��

7���M(j��n)��ܛ�����b���ȴ����b��ɾͿ����ˡ�

1�M���ƽ̌W(xu��)ͨ2.0-�M���ƽ̌W(xu��)ͨ2.0���d v5......

2step7 microwin-���T��PLC S7......

3�ٶȾW(w��ng)�P��ˬ����������-�W(w��ng)�P����-�ٶȾW(w��ng)�P��ˬ��......

4360��ȫ�g�[��-�g�[��-360��ȫ�g�[�����d ......

5�ȸ�g�[�� XP��-�ȸ�g�[�� XP��-�ȸ�g�[......

6Kittenblock�ؑc�������ð�-�C(j��)���˾���......

7seo�������(�������) -SEO��會�(y��u)������......

8Notepad3-ӛ�±�ܛ��-Notepad3��......

9С���\(y��n)��ˢ����(sh��)����-С���\(y��n)��ˢ����(sh��)�������d v2......

1����\(y��n)��GHOST���bϵ�y(t��ng),��������\(y��n)���R���b�C(j��)

2Ů����ɶ���^��ã��m��Ů���\(y��n)�õ����^��_��

3���Ľ�����ΰ��bghostxpϵ�y(t��ng)

4�o�����(bi��o)�p�ĵĎNԭ�� �Լ�̎������

5Windows��������Win10ʧ����ʾ0x80...

6����Windows10 1607�汾�ľ��w�O(sh��)�÷�...

7win10��X�桶ֲ����(zh��n)��ʬ���W�˵�̎���k��

82018������^����ɶ��2018���Ů��...